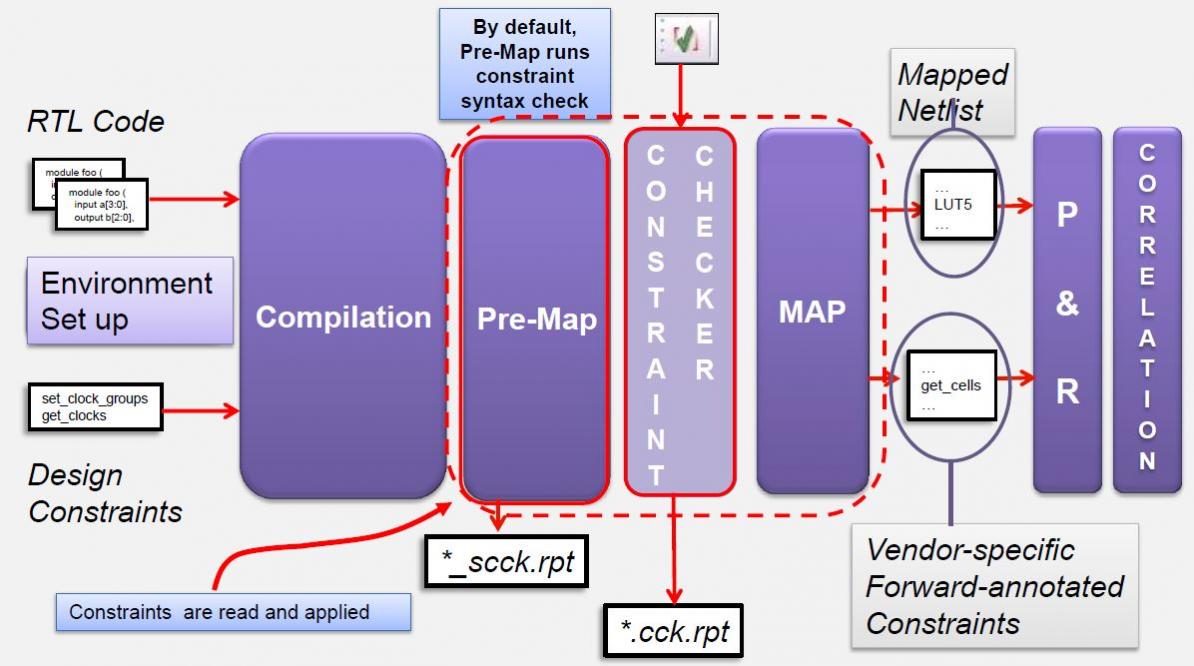

Here wire_clk90 is derived clock from clkin. TIMESPEC "TS_wire_clk90" = PERIOD "wire_clk90" "TS_clkin" * 2 PHASE + 12.5 ns TIMESPEC "TS_clkin" = PERIOD "clkin" 20 MHz HIGH 50 % Here the clk_1 is the base clock and clk_2_s is the derived clock.clk_2 is half the frequency of clk_1.here clk_2_s is not in the port its an internal clock. TIMESPEC "TS_clk_2_s" = PERIOD "clk_2_s" "TS_clk_1" / 2 PHASE + 0 ns To continue with the Synplify design flow, generate Verilog Quartus Mapping Files with the Synplify software.TIMESPEC "TS_clk_1" = PERIOD "clk_1" 20 MHz HIGH 50 % If you add timing constraints or resource assignments in a separate Synplify Design Constraints File, you must add the Synplify Design Constraints File to the Source Files list in the Synplify window by using the SCOPE constraint editor.

Important: Constraint modifications should be made with the SCOPE constraint editor rather than editing the Synplify Design Constraints File, Synopsys Constraints Format File, or Tcl Script File.

Synplify pro clock constraint software#

The Synplify software then uses the values in the SDC File when it creates the. You can specify the f MAX timing requirement in the Synplify software and add the DEFINE_INPUT_DELAY and DEFINE_OUTPUT_DELAY variables in the Synplify Design Constraints File. If you use the TimeQuest Timing Analyzer, Synplify can write and annotate timing constraints in the Synopsys Constraints Format File (.scf).

Synplify incorporates attributes that are applicable to the Quartus II software into a. Output sum /* synthesis */ ĭefine_attribute altera_chip_pin_lc appropriate timing constraints in a separate Synplify Design Constraints File or in the VHDL or Verilog HDL source file. Refer to the following table for the correct syntax on making pin assignments in Verilog HDL and VHDL design files and Synplify Design Constraints Files:Īttribute altera_chip_pin_lc of : signal is " Īttribute altera_chip_pin_lc of result : signal HDL Select altera_chip_pin_lc in the Attribute column. Select the pin for which you wish to make the assignment in the Object column. To make pin assignments using the Synplify software: You can specify pins in VHDL or Verilog HDL designs, or in a Synplify Design Constraints File. You can assign a single port to a specific pin to ensure that the signal is always associated with that pin, regardless of future changes to a project. If you have not already done so, perform Setting Up a Project in the Synplify Software. To specify design constraints in the Synplify software: If you add timing constraints or resource assignments in a separate Synplify Design Constraints File, you must add the Synplify Design Constraints File to the project by adding it to the Source Files list in the Synplify window. tcl file targeted to any Altera device supported by the Quartus II software. The Synplify software automatically incorporates these attributes into a Tcl Script File (. When you use the Synplify software, you can assign a limited subset of Quartus II resource assignments by specifying attributes in the Synplify Design Constraints File (. Assigning Design Constraints with the Synplify SoftwareĪssigning design constraints in the Synopsys Synplify software includes specifying pin assignments, timing constraints, and other resource assignments.